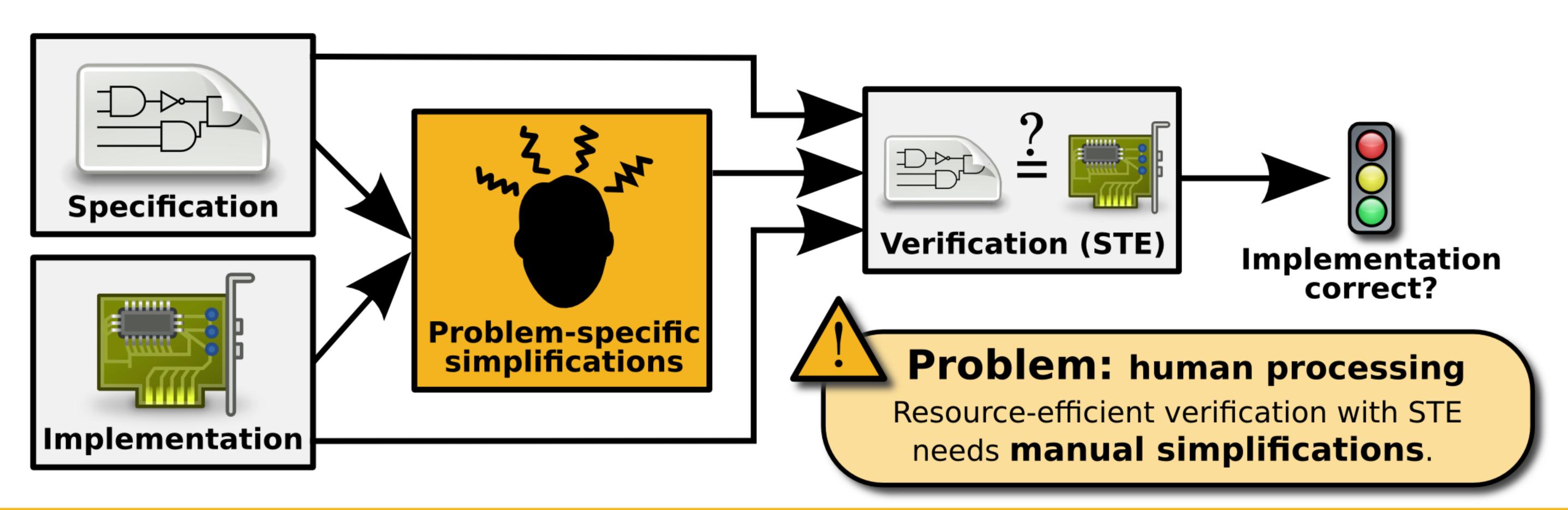

## **Automating Hardware Verification**

## Our Contribution: automatic simplifications

Goal: Reduce number of cases the verification needs to examine

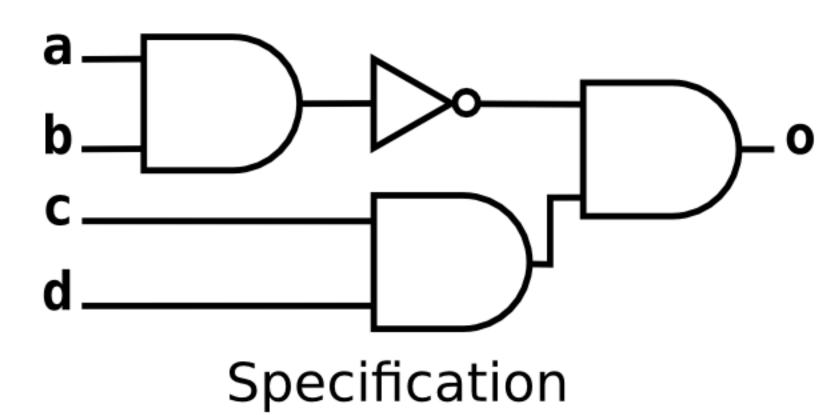

Idea: Determine which partial input combinations lead to a concrete output

**Method:** Work through the specification from the outputs to the inputs:

determine the different scenarios that lead to a true or false output by propagating backwards which input stimuli are required in each step

**Example:**

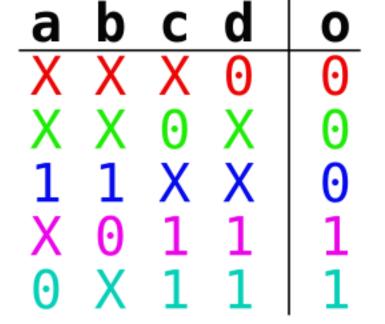

before: 16 scenarios now: 5 scenarios

Partial input combinations

Sufficiency: Partial input combinations cover all possible cases

| 0100 | 1000 | 0110 | 1010 |

|------|------|------|------|

| 0000 | 1100 | 1110 | 0010 |

| 0001 | 1101 | 1111 | 0111 |

| 0101 | 1001 | 1011 | 0011 |

Our automatic simplifications cover all cases by construction. Manual simplifications have to be checked for full coverage.

## Results: correct simplifications that enable the verification of more circuits

1.

2.

5

| 3. | 0100 | 1000 | 0110 | 1010 |  |

|----|------|------|------|------|--|

|    | 0000 | 1100 | 1110 | 0010 |  |

|    | 0001 | 1101 | 1111 | 0111 |  |

|    | 0101 | 1001 | 1011 | 0011 |  |

automatic simplifications as good as known manual ones

generates simplifications where no manual ones exist

automatic simplifications correct by construction

## OXFORD UNIVERSITY COMPUTING LABORATORY